# ADVANCING COMPILER OPTIMIZATIONS FOR GENERAL-PURPOSE & DOMAIN-SPECIFIC PARALLEL ARCHITECTURES

A Dissertation Presented to The Academic Faculty

By

Prasanth Chatarasi

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Computer Science

Georgia Institute of Technology

December 2020

Copyright © Prasanth Chatarasi 2020

# ADVANCING COMPILER OPTIMIZATIONS FOR GENERAL-PURPOSE & DOMAIN-SPECIFIC PARALLEL ARCHITECTURES

Approved by:

Dr. Vivek Sarkar, Advisor School of Computer Science *Georgia Institute of Technology*

Dr. Jun Shirako, Co-Advisor School of Computer Science *Georgia Institute of Technology*

Dr. Santosh Pande School of Computer Science *Georgia Institute of Technology*  Dr. Tushar Krishna School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Richard Vuduc School of Computational Science and Engineering *Georgia Institute of Technology*

Date Approved: July 27, 2020

"Dream the impossible. Know that you are born in this world to do something wonderful and unique; don't let this opportunity pass by. Give yourself the freedom to dream and think big." — Sri Sri Ravi Shankar To universal consciousness, To my family, To my advisors, mentors, teachers, and friends.

#### ACKNOWLEDGEMENTS

# Taittiriya Upanishad, Shikshavalli I.20 मात्रुदेवो भव पित्रुदेवो भव आछार्यदेवो भव अतिथिदेवो भव

mātrudevo bhava pitrudevo bhava āchāryadevo bhava atithidevo bhava "Respects to Mother, Father, Guru, and Guest. They are all forms of God".

First and foremost, I would like to express my gratitude to my mother *Ch. Anjanee Devi* and my father *Dr. C. V. Subbaiah* for always being there for me, and loving me unconditionally throughout the situations of extreme happiness to sadness. Without the two of you, I don't know where I would be. If I have learned anything while being away from you, it is that you are the most important people in my life, and I love you both more than anything.

I want to express my sincere appreciation to my guru (advisor) *Prof. Vivek Sarkar*, who always had time for me when I needed him – no matter whether the reason was a technical discussion, an administrative problem, academic development, or the planning of my next steps. There are no words that can express my gratitude towards your efforts. Thank you for believing in me and supporting me. Without you, I would not be able to handle everything that the graduate program and life threw. Having you backing me up 100% allows me to be at peace and do research. You're much more than an advisor, and thanks for helping me in my personal life too. Thanks for being my inspiration in the path of being a useful scientific researcher to this world.

I am also very grateful to my co-advisor *Dr. Jun Shirako*, with whom I had many very fruitful discussions on various topics of this thesis. Thank you for always being supportive, even when I feel like I can't do it. Thank you for being a humble teacher in explaining the answers to my questions – Arigatou Gozaimasu! The lunch sessions were great to discuss my ideas and build a relationship with you.

I want to thank the rest of my committee *Prof. Tushar Krishna*, *Prof. Santosh Pande*, and *Prof. Rich Vuduc* for agreeing to be part of my thesis committee. I thank you all for your time, feedback, and suggestions in significantly improving the thesis. I always had a great time interacting with you at the school corridors, labs, and conferences. I am very fortunate to collaborate with Tushar Krishna's group, and thanks, Tushar, for being an integral part of my Ph.D. journey, including the job search.

I'm also very grateful to my collaborators, i.e., Albert Cohen from INRIA/Google AI, Tushar Krishna and Hyoukjun Kwon from Synergy Research Group, Angshuman Parashar and Micheal Pellauer from NVIDIA Architecture Research Group, Stephen Neuendorffer, Samuel Bayliss, and Kees Vissers from Xilinx Research Labs, Karthik Murthy from Google AI, and John Mellor-Crummey from Rice University. Thanks for enriching my research experience in the Ph.D. journey, including asking the right questions, thinking critically, positioning the work, writing research papers, giving a broader perspective of the researcher, and so on. I also want to acknowledge the Habanero Extreme Scale Software Research Group, Synergy Research Group, and CRNCH Research Center (Jeffery Young and Jason Riedy) for the research interactions in my Ph.D. journey.

In addition to the collaborators mentioned above, I also want to acknowledge and appreciate my mentors, especially Dr. Milind Chabbi, Dr. Shams Imam, Dr. Deepak Majeti, and Dr. Rishi Surendran for all the helpful advice in both research and personal life. I cannot thank you enough for everything you taught me during my Ph.D. journey. I greatly value your kindness and the expertise you imparted to me as my mentors.

I want to acknowledge my professor *Prof. Kesav Nori* for piquing my curiosity about compilers during my undergraduate study at IIT Hyderabad. Without you, I would not be where I am today. Also, thanks are due to my bachelor thesis advisors Dr. Aditya Nori, Prof. M. V. Panduranga Rao and Prof. Bheemarjuna Reddy for giving me a research exposure in the undergraduate study. Thanks to all my professors who encouraged me to apply for graduate studies and quickly provide reference letters.

Thanks are due to my friends for all the support and encouragement during my stay at Georgia Tech. There are too many of you to mention, but I would especially like to thank Prithayan Barua, Pramod Chunduri, Poulami Das, Anirudh Jain, Hyoukjun Kwon, Ankush Mandal, Girish Mururu, Mayank Parasar, Sriraj Paul, Christopher Porter, Gururaj Saileshwar, Anand Samajdar, Srisehan Srikanth, Kavitha Sthanam, Lechen Yu, and Jimmy Zhong. Thanks for always being up for a good laugh over the years. I would also like to thank the School of Computer Science department staff members for all the help I received during my stay at GaTech, including Ruthie Book and Wanda Purinton.

Also, I want to acknowledge Sharon Riehl for being the coach in my leadership development as part of the Georgia Tech Leading Edge program and helping me to self-analyze and improve in many aspects, including establishing trust and taking and giving constructive feedback, and prioritization. Furthermore, an essential aspect of my Ph.D. journey is the association with the SKY meditation club at GaTech and also the Art of Living foundation. The association helped me much towards the spiritual path and also managing of my mental health – in that regards, I want to acknowledge many people, especially my teachers Sareena Nagpal, Rachana Gadhok, Kunwar Gadhok, Preeti Bhatt.

The acknowledgments never end without mentioning siblings, i.e., my elder sister Sree Pavani and my elder brother Sreenivas. First and for most, life may not be that exciting without you. We may fight 50% of the time, but I love you a lot for being my best friends, toughening up during tough situations of my life, and celebrating with me during happy moments. As per a Vietnamese proverb, you both are as close as my hands and feet. Also, my life has been more beautiful with my two nieces, i.e., Venkata Tejaswini and Sai Sughandhini – I always felt content hearing the word "mamayya" from them.

"Gratitude to the entire creation for showering a lot of love, grace, and blessings!".

## TABLE OF CONTENTS

| List of ' | Fables .  | xiv                                    |

|-----------|-----------|----------------------------------------|

| List of ] | Figures   |                                        |

| Summa     | ry        |                                        |

| Chapte    | r 1: Inti | roduction                              |

| 1.1       | Thesis    | Statement                              |

| 1.2       | Contril   | putions                                |

| 1.3       | Organi    | zation                                 |

| Chapte    | r 2: Bac  | <b>kground</b>                         |

| 2.1       | Paralle   | l Architectures                        |

|           | 2.1.1     | General-Purpose Parallel Architectures |

|           |           | Multi-Core Architectures               |

|           |           | Vector Processing (SIMD) Architectures |

|           | 2.1.2     | Domain-Specific Parallel Architectures |

|           |           | Spatial DNN Accelerators               |

|           |           | Specialized Vector Processing Units    |

|           |           | Thread Migratory Architectures         |

| 2.2    | High-l              | Performance Applications                                     | 17 |

|--------|---------------------|--------------------------------------------------------------|----|

|        | 2.2.1               | Scientific Computing Applications                            | 17 |

|        | 2.2.2               | Deep Learning                                                | 17 |

|        | 2.2.3               | Graph Analytics                                              | 19 |

| 2.3    | Summ                | ary                                                          | 19 |

| Chapte | r 3: Po             | PP: Polyhedral Optimizations of Explicitly-Parallel Programs | 20 |

| 3.1    | Abstra              | nct                                                          | 20 |

| 3.2    | Introd              | uction                                                       | 21 |

| 3.3    | Backg               | round                                                        | 22 |

|        | 3.3.1               | Polyhedral Model                                             | 22 |

|        | 3.3.2               | Explicit Parallelism                                         | 23 |

|        |                     | Loop-level parallelism                                       | 24 |

|        |                     | Task-level parallelism including dependences                 | 24 |

| 3.4    | Motivating Examples |                                                              |    |

|        | 3.4.1               | 2-D Jacobi                                                   | 25 |

|        | 3.4.2               | Particle Filter                                              | 26 |

| 3.5    | Polyhe              | edral optimizer for Parallel Programs (PoPP)                 | 26 |

|        | 3.5.1               | Conservative analysis                                        | 28 |

|        | 3.5.2               | Extraction of happens-before relations                       | 30 |

|        |                     | Loop-level parallelism                                       | 30 |

|        |                     | Task parallelism including dependences                       | 31 |

|        | 3.5.3               | Reflection of happens-before relations                       | 33 |

|        | 3.5.4   | PolyAST: a loop optimizer integrating polyhedral and AST-based transformations | 34 |

|--------|---------|--------------------------------------------------------------------------------|----|

| 3.6    | Experi  | mental Evaluation                                                              | 35 |

|        | 3.6.1   | Experimental setup                                                             | 35 |

|        | 3.6.2   | KASTORS Suite                                                                  | 39 |

|        | 3.6.3   | Rodinia Suite                                                                  | 40 |

| 3.7    | Limita  | tions                                                                          | 41 |

| 3.8    | Relate  | d Work                                                                         | 42 |

| 3.9    | Summ    | ary                                                                            | 43 |

| Chapte |         | ySIMD: A Unified Approach to Variable Renaming for Enhanced                    | 45 |

| 4.1    | Abstra  | ct                                                                             | 45 |

| 4.2    | Introdu | uction                                                                         | 46 |

| 4.3    | Discus  | ssion on Variable Renaming Transformations                                     | 48 |

|        | 4.3.1   | Source Variable Renaming (SoVR)                                                | 49 |

|        | 4.3.2   | Sink Variable Renaming (SiVR)                                                  | 50 |

|        | 4.3.3   | Synergy between SoVR and SiVR                                                  | 51 |

| 4.4    | Motiva  | ating Example                                                                  | 51 |

| 4.5    | Our U   | nified Approach to Variable Renaming                                           | 53 |

|        | 4.5.1   | Dependence Cycles Finder                                                       | 53 |

|        | 4.5.2   | Bipartite Graph Constructor                                                    | 55 |

|        | 4.5.3   | Solver                                                                         | 55 |

|        | 4.5.4   | Transformer                                                                    | 57 |

|        | 4.5.5  | Bounding Additional Space                                              | 57 |  |

|--------|--------|------------------------------------------------------------------------|----|--|

| 4.6    | Perfor | mance Evaluation                                                       | 58 |  |

|        | 4.6.1  | Experimental Platforms                                                 | 58 |  |

|        | 4.6.2  | Benchmarks                                                             | 59 |  |

|        | 4.6.3  | Comparison with ICC                                                    | 60 |  |

|        | 4.6.4  | Comparison with Calland et al's approach                               | 62 |  |

|        | 4.6.5  | Comparison with Chu et al's approach                                   | 62 |  |

| 4.7    | Relate | d Work                                                                 | 63 |  |

| 4.8    | Summ   | ary                                                                    | 64 |  |

| Chapto |        | urvel: A Data-centric Compiler for DNN Operators on Spatial celerators | 66 |  |

| 5.1    | Abstra | ct                                                                     | 66 |  |

| 5.2    | Introd | uction                                                                 | 67 |  |

| 5.3    | Backg  | Background                                                             |    |  |

|        | 5.3.1  | Spatial DNN Accelerators                                               | 70 |  |

|        | 5.3.2  | MDC Notation                                                           | 71 |  |

| 5.4    | Confo  | rmable DNN Operators                                                   | 73 |  |

| 5.5    | Transf | ormation                                                               | 76 |  |

|        | 5.5.1  | Data Mapping directives                                                | 77 |  |

| 5.6    | Mappi  | ng Space Exploration                                                   | 80 |  |

|        | 5.6.1  | Solving off-chip mapping subspace                                      | 81 |  |

|        | 5.6.2  | Solving on-chip mapping subspace                                       | 83 |  |

| 5.7    | Evalua | ution                                                                  | 84 |  |

|        | 5.7.1  | Evaluation on CONV2D                                                                           |

|--------|--------|------------------------------------------------------------------------------------------------|

|        | 5.7.2  | Evaluation on GEMM                                                                             |

|        | 5.7.3  | Evaluation on MLP and LSTM                                                                     |

| 5.8    | Relate | d Work                                                                                         |

| 5.9    | Summ   | ary                                                                                            |

| Chapte | •      | asa: A High-Performance Vectorizing Compiler for Tensor Con-<br>utions on the Xilinx AI Engine |

| 6.1    | Abstra | ict                                                                                            |

| 6.2    | Introd | uction                                                                                         |

| 6.3    | Backg  | round                                                                                          |

|        | 6.3.1  | Tensor Convolutions                                                                            |

|        | 6.3.2  | Xilinx AI Engine                                                                               |

| 6.4    | Our A  | pproach                                                                                        |

|        | 6.4.1  | Translating into Triplet Representation                                                        |

|        | 6.4.2  | Lazy Stores Optimization                                                                       |

|        | 6.4.3  | Exploiting Vector Register Reuse & Realizing Unaligned Loads<br>and Scalar Broadcast           |

|        | 6.4.4  | 2D Vector SIMD Datapath                                                                        |

|        | 6.4.5  | Code Generation                                                                                |

|        | 6.4.6  | Auto-tuner                                                                                     |

| 6.5    | Experi | ments                                                                                          |

|        | 6.5.1  | CONV2D in Computer Vision                                                                      |

|        | 6.5.2  | CONV2D in Deep Learning                                                                        |

|         | 6.5.3 CONV3D                                                                                |

|---------|---------------------------------------------------------------------------------------------|

| 6.6     | Related Work                                                                                |

| 6.7     | Summary                                                                                     |

| Chapte  | 7: Compiler Optimizations for Graph Analytics on a Thread Migra-<br>tory Architecture (EMU) |

| 7.1     | Abstract                                                                                    |

| 7.2     | Introduction                                                                                |

| 7.3     | Compiler Transformations                                                                    |

|         | 7.3.1 Node/Loop Fusion                                                                      |

|         | 7.3.2 Edge Flipping                                                                         |

|         | 7.3.3 Use of Remote Updates                                                                 |

| 7.4     | Experiments                                                                                 |

|         | 7.4.1 Experimental Setup                                                                    |

|         | 7.4.2 Conductance algorithm                                                                 |

|         | 7.4.3Single Source Shortest Path using Bellman-Ford's Algorithm (SSSP-BF)BF)                |

|         | 7.4.4 Triangle Counting Algorithm                                                           |

| 7.5     | Related Work                                                                                |

| 7.6     | Summary                                                                                     |

| Chapte  | 8: Conclusions and Future Directions                                                        |

| Referen | <b>ces</b>                                                                                  |

## LIST OF TABLES

| 3.1 | Details of architectures used for experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Sequential execution times of KASTORS and Rodinia on Intel Westmere<br>and IBM Power 8 systems along with problem sizes. Intel ICC-14.0 com-<br>piler doesn't support OpenMP 4.0 task depend constructs. So, no execution<br>time is reported for KASTORS on Intel platform with ICC compiler. Trans-<br>formations exposed by PoPP: Permutation (P), Fusion (F), Skewing (S),<br>Tiling (T), Doacross pipelined parallelism (D), No further optimizations (-).<br>Manual modifications performed before passing to PoPP: Replace complex<br>if-statements by closures i.e., outlined functions (OF), Delinearization on<br>task-depend variables (D), Function inlining (F), Annotated inner loop as<br>parallel (AP), Annotated inner loop as parallel with array reductions (APR),<br>Annotated with task-depend constructs (AT), Removal of printf statements<br>(R), No modifications (-). | 36 |

| 4.1 | A comparison between SoVR and SiVR transformations related to the space requirements and additional stores, loads introduced by these transformations in one iteration of the target loop. * – Additional scalar loads/stores for SiVR transformation may go negative in case of renaming scalars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51 |

| 4.2 | Bipartite graph constructed on the dependence graph of the original pro-<br>gram in Figure 4.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54 |

| 4.3 | Summary of SIMD architectures and compiler flags used in our experi-<br>ments. SP refers to Single Precision floating point operands, VPU refers to<br>a KNL Vector Processing Unit, and SM refers to a GPU Streaming Multi-<br>processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59 |

| 4.4 | Summary of the 11 benchmarks from the TSVC suite used in our eval-<br>uation, including the number of statements, number of dependences, and<br>number of elementary cycles per benchmark (excluding self-loop cycles).<br>The benchmarks were executed using $N = 2^{25}$ and $T = 200$ as input parame-<br>ters. Number of SiVR and SoVR transformations performed by <i>PolySIMD</i><br>for the 11 benchmarks, and also the overall compilation times required.<br>Coincidentally, none of these benchmarks triggered a case in which both<br>SiVR and SoVR transformations had to be performed | 60  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.5 | Speedups on the Intel KNL processor and NVIDIA Volta accelerator using <i>PolySIMD</i> on seven benchmarks from the eleven benchmarks relative to past approaches, i.e., Calland et al. [29] and Chu et al. [30]. We excluded the remaining four benchmarks from the table since our results were similar to both of the past works.                                                                                                                                                                                                                                                               | 62  |

| 5.1 | Conformability of the popular DNN operators onto the MDC notation (Y/N refers to YES/NO).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76  |

| 5.2 | DNN primitive operators, occurrences, and MDC conformability in the MLPerf [147] DNN models, VGG16, and AlexNet models                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77  |

| 5.3 | Accelerator setups in our evaluation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84  |

| 5.4 | The statistics (min/avg/max) of the CONV2D mapping space in our eval-<br>uation and the resultant mapping subspaces after decoupling and pruning<br>strategies.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87  |

| 5.5 | Two layers from VGG16 and MobileNetV2 for brief discussion on our approach generated mappings; Level-3 tile sizes and degree of parallelism are part of the mappings identified by our approach on Platform P2                                                                                                                                                                                                                                                                                                                                                                                     | 88  |

| 5.6 | Description of the GEMM workloads taken from the recent work in [154]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 89  |

| 5.7 | Description of the MLP and LSTM workloads taken from the Interstellar work in [136]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90  |

| 5.8 | Comparison of our MDC notation with prior compilers in terms of expres-<br>siveness, mapping notation, and the presence of accurate cost models                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92  |

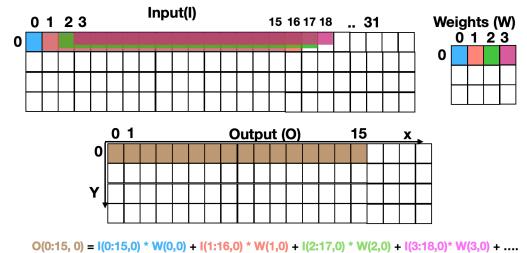

| 6.1 | Triplet representation of the loop body in Figure 6.3(c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 103 |

| 6.2 | Triplet representation after the lazy stores optimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104 |

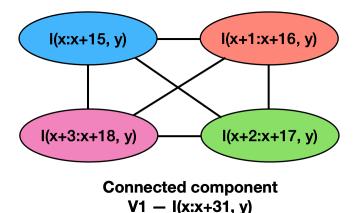

| 6.3 | Triplet representation after addressing unaligned loads, scalar broadcast, and exploiting vector register reuse                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.4 | Triplet representation after fusing the logical 1D vector multiplications and finding the data selection parameters                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.5 | The AI Engine configuration used in our evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6.6 | CONV2D workloads of Computer Vision used in our evaluation and opti-<br>mal schedules from auto-tuner                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.7 | CONV2D workloads of deep learning used in our evaluation (variable names described in Section 6.3) and optimal schedules                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.1 | Specifications of a single node of the Emu system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.2 | Experimental evaluation of three graph algorithms (Conductance, SSSP-BF and Triangle counting) on the RMAT graphs from scales 6 to 14 specified by Graph500. Transformations applied on the algorithms: Conductance/SSSP-BF/Triangle counting: (Node fusion)/(Edge flipping and Remote updates)/ (Remote updates). The evaluation is done a single node of the Emu system described in Table 7.1. Note that we had intermittent termination issues while running SSSP-BF from scale 13-14 on the Emu node, and hence we omitted its results |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# LIST OF FIGURES

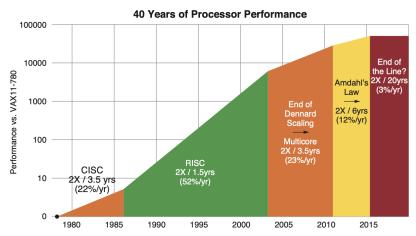

| 1.1 | 40 years of process performance (taken from [6, 7])                                                                                                                                                                                      | 1     |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|

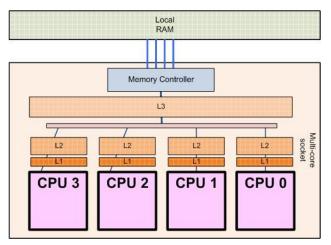

| 2.1 | An abstract overview of a general-purpose multi-core processor having multiple CPUs with a memory hierarchy (figure source: [38])                                                                                                        | 11    |    |

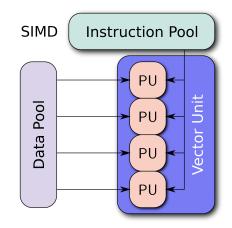

| 2.2 | An abstract overview of a general-purpose SIMD architecture (figure source: [3                                                                                                                                                           | 39]). | 12 |

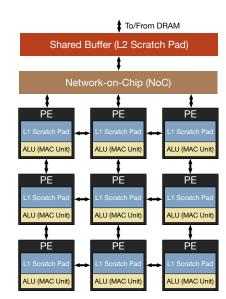

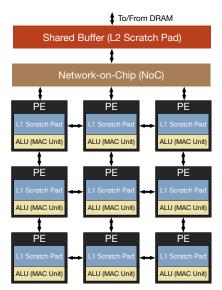

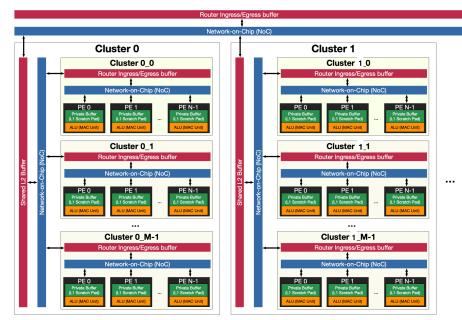

| 2.3 | An abstract overview of a spatial DNN accelerator model which is pervasive in many state-of-the-art accelerators [40, 41, 42, 43, 44]                                                                                                    | 13    |    |

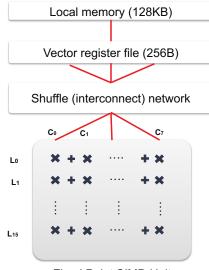

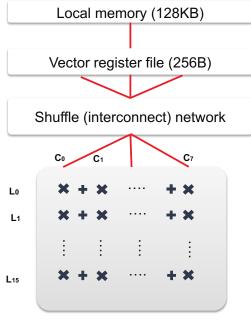

| 2.4 | An abstract overview of a specialized vector processing unit in the Xilinx AI Engine                                                                                                                                                     | 15    |    |

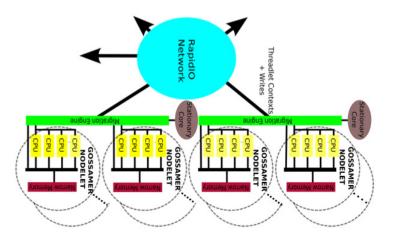

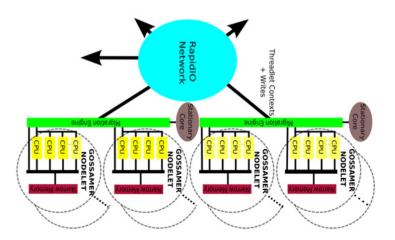

| 2.5 | An abstract overview of a thread migratory architecture in the EMU (figure source: [53]).                                                                                                                                                | 16    |    |

| 3.1 | 2-D Jacobi kernel from KASTORS suite.                                                                                                                                                                                                    | 25    |    |

| 3.2 | Particle filter kernel from Rodinia suite                                                                                                                                                                                                | 27    |    |

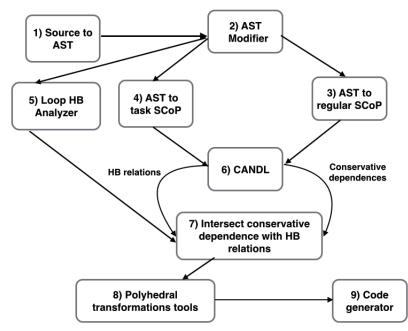

| 3.3 | Overview of our approach                                                                                                                                                                                                                 | 28    |    |

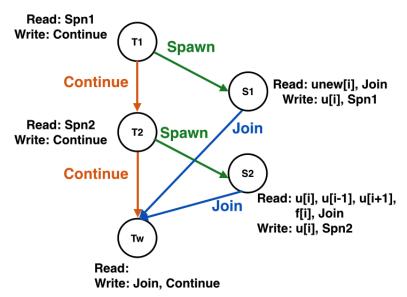

| 3.4 | Happens-before relations for the Jacobi program in Figure 3.5(a) due to task-spawn, task-wait, and sequential ordering                                                                                                                   | 31    |    |

| 3.5 | Overall explanation of our framework on Jacobi benchmark from KAS-<br>TORS suite                                                                                                                                                         | 32    |    |

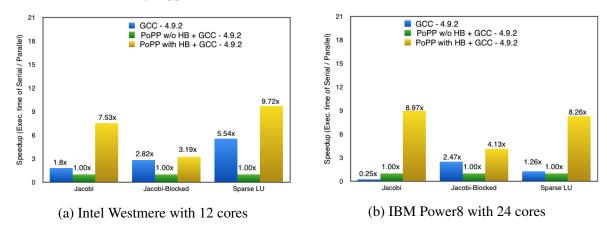

| 3.6 | Evaluation of the KASTORS suite (using GCC compiler). Sequential times are reported in Table 3.2. Original benchmark speedup is compared against with optimized codes from PoPP with/ without considering happens-before (HB) relations. | 37    |    |

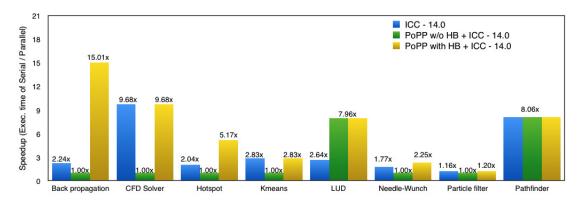

| 3.7 | Evaluation of the Rodinia suite (using Intel compiler) on Intel Westmere with 12 cores. Sequential times are reported in Table 3.2. Original benchmark speedup is compared against with optimized codes from PoPP with/ without considering happens-before (HB) relations                                      | 37 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

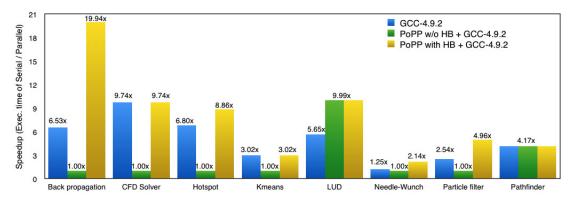

| 3.8 | Evaluation of Rodinia suite (using GCC compiler) on Intel Westmere with 12 cores. Sequential times are reported in Table 3.2. Original benchmark speedup is compared against with optimized codes from PoPP with/ without considering happens-before (HB) relations.                                           | 38 |

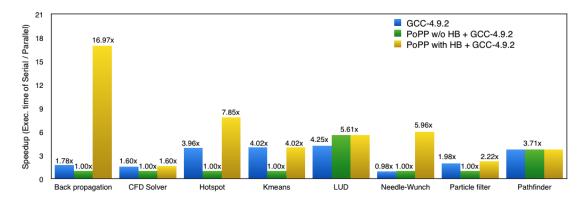

| 3.9 | Evaluation of the Rodinia suite (using GCC compiler) on IBM Power8 with 24 cores. Sequential times are reported in Table 3.2. Original benchmark speedup is compared against with optimized codes from PoPP with/ without considering happens-before (HB) relations.                                           | 38 |

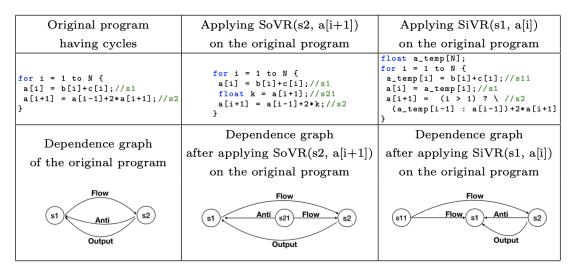

| 4.1 | An example to illustrate SoVR and SiVR transformations                                                                                                                                                                                                                                                         | 48 |

| 4.2 | A running example from [29] whose dependence graph consists of three cycles c1/c2/c3: s1-s3-s2-s4-s1/s1-s3-s4-s1/s1-s2-s4-s1 which prohibit vectorization. The table also lists dependence graphs and transformed codes after applying past approach [29] and our integrated approach on the original program. | 52 |

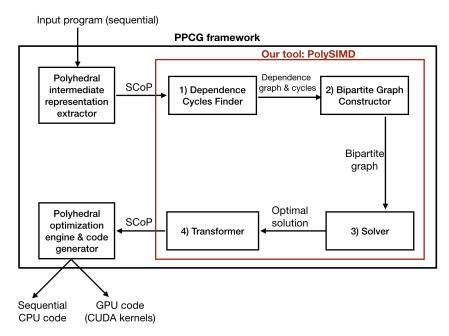

| 4.3 | Workflow of <i>PolySIMD</i> implemented as an extension to the PPCG [114]                                                                                                                                                                                                                                      | 53 |

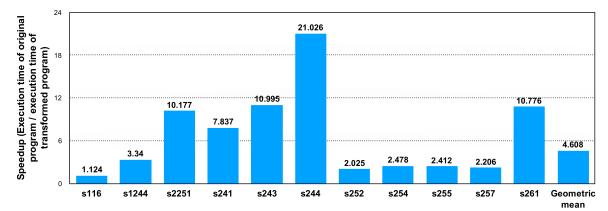

| 4.4 | Speedups using <i>PolySIMD</i> on the eleven benchmarks from the TSVC suite, compiled using the Intel's ICC v17.0 product compiler and running on a single core of Intel Knights Landing processor.                                                                                                            | 59 |

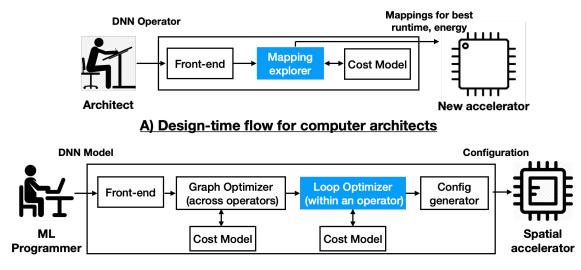

| 5.1 | Overview of the design-time flow for computer architects developing new accelerators, and the compilation flow for ML programmers leveraging the accelerators. Scope of this work is the mapping explorer and the loop optimizer in the above diagram.                                                         | 67 |

| 5.2 | Abstract spatial accelerator model which is pervasive in many state-of-the-<br>art accelerators [40, 46, 144, 43].                                                                                                                                                                                             | 70 |

| 5.3 | A broader overview of a spatial accelerator system having multiple accelerators in the form of clusters.                                                                                                                                                                                                       | 70 |

| 5.4 | A mapping of the CONV1D in the MDC notation along with the visualiza-<br>tion of its data mappings.                                                                                                                                                                                                            | 72 |

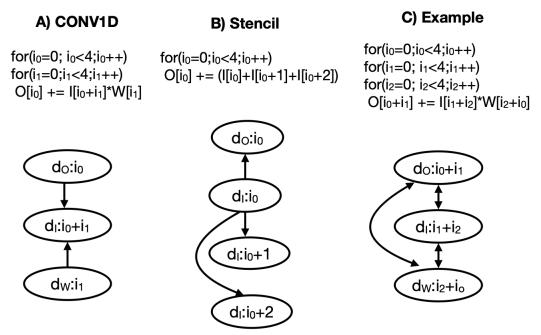

| 5.5  | The dimension dependence graph (DDG) of simple operators such as CONV1D and stencil satisfying the rule R3, and an example violating the rule R3. $d_O/d_I/d_W$ : tensor dimension variables corresponding to the output, input, and weight tensors.                                                                                                  | <b>)</b><br>74 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

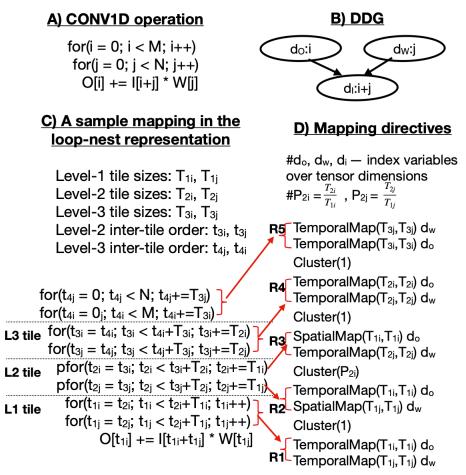

| 5.6  | A brief overview of the mapping expressed in the loop-nest form of CONV1D, and its translation into the MDC notation with data mapping directives                                                                                                                                                                                                     | 79             |

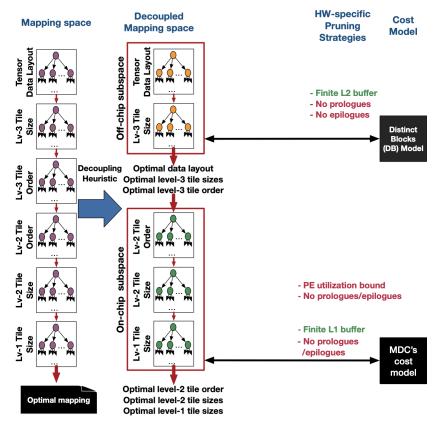

| 5.7  | An overview of our approach along with pruning strategies for searching mapping space of convolutions. The pruning strategies in green color preserve optimal mappings, whereas the strategies in red color may prune optimal.                                                                                                                        | 81             |

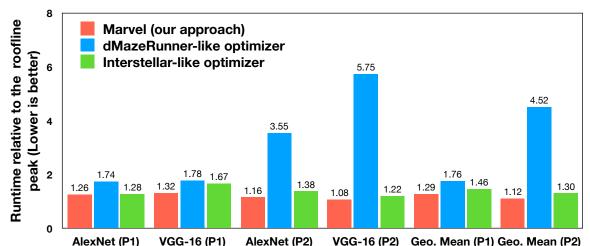

| 5.8  | Performance comparison of Marvel generated mappings with the mappings of dMazeRunner-like optimizer [135] and Interstellar-like optimizer [136] relative to the roof-line peaks of the AlexNet and VGG-16 models on both the platforms (P1 and P2)                                                                                                    | 85             |

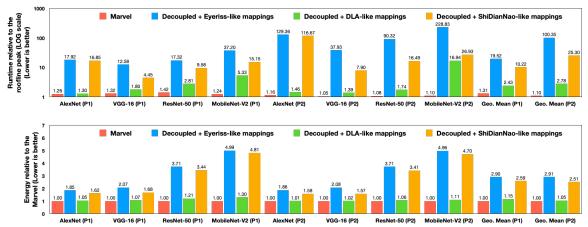

| 5.9  | Runtime and energy comparison of Marvel generated mappings with the popular mapping styles such as row-stationary (RS) from Eyeriss [40], weight-stationary from DLA [46], output-stationary from ShiDianNao [145] for the AlexNet [64], VGG-16 [65], ResNet-50 [137], MobileNet-V2 [138] models on both the platforms (P1 and P2).                   | 86             |

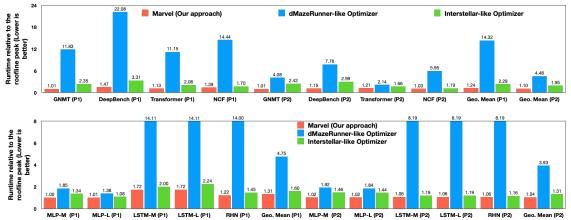

| 5.10 | Performance comparison of Marvel generated mappings with the mappings of dMazeRunner-like optimizer [135], and Interstellar-like optimizer [136] relative to the roof-line peaks of the GEMM workloads in Table 5.6 and LSTM, MLP in Table 5.7 on both the platforms (P1 and P2).                                                                     | 91             |

| 5.11 | Comparison of Marvel with prior compiler approaches for spatial acceler-<br>ators (mRNA [139], Zhang et al. [132], Ma et al. [131], Auto-TVM [76],<br>dMazeRunner [135], Interstellar [136], TimeLoop [133]) for the mapping<br>space exploration of DNN operators. Our approach (Marvel) supports any<br>operator conformable with the MDC notation. | 93             |

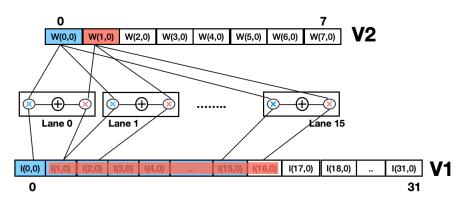

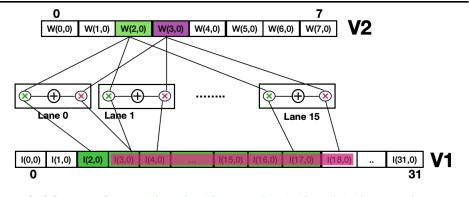

| 6.1  | A pictorial overview of the key architectural features of the Xilinx AI En-<br>gine, i.e., 2D vector SIMD datapath and shuffle network.                                                                                                                                                                                                               | 99             |

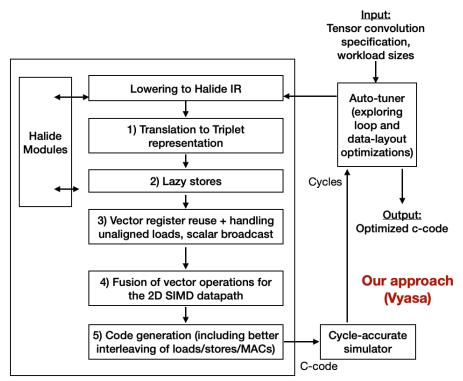

| 6.2  | Workflow of our approach (Vyasa) which is implemented as an extension to the Halide framework [70]                                                                                                                                                                                                                                                    | 101            |

| 6.3  | Algorithmic description of the convolution of a $4x3$ filter over an input 2D image in the Halide language [70]. A(a:b,c) is a short hand vector notation for denoting a contiguous slice from A(a,c) to A(b,c) in one direction 1                                                                                                                    | 102            |

| 6.4  | A pictorial overview of the convolution of $4x3$ filter based on the schedule described in Figure 6.3(b) at the loop iterations $x = 0$ and $y = 0$ 102                                                                                                                                                                                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.5  | Reuse graph corresponding to the vector loads of the tensor I in Table 6.2, and its connected components to construct larger vector loads 105                                                                                                                                                                                                                                          |

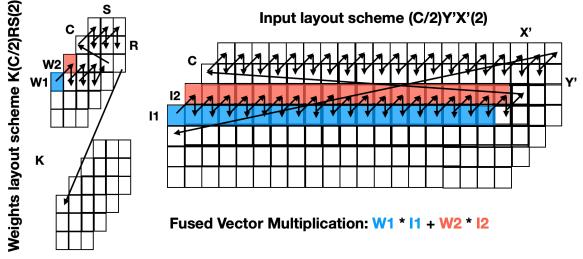

| 6.6  | An overview of the two fused vector operations (a and b) over the vector registers V1, V2 for input and weights, respectively of the running example shown in Table 6.2 at $x=0$ and $y=0$ . The shuffle network of the AI Engine helps each multiplier of the 16 lanes and 2 columns of the 2D SIMD datapath to choose required elements from the vector registers 107                |

| 6.7  | A snippet of the generated 16-bit vector code for the running example<br>in Figure 6.3. VLOAD/VMUL/VMAC/VSTORE refers to vector load, vec-<br>tor multiplication, vector multiply-and-accumulate, and vector store. SE-<br>LECT symbolically represents the data selection over a vector register for<br>the i <sup>th</sup> row and j <sup>th</sup> column of 2D datapath multipliers |

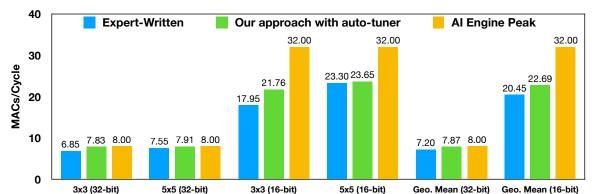

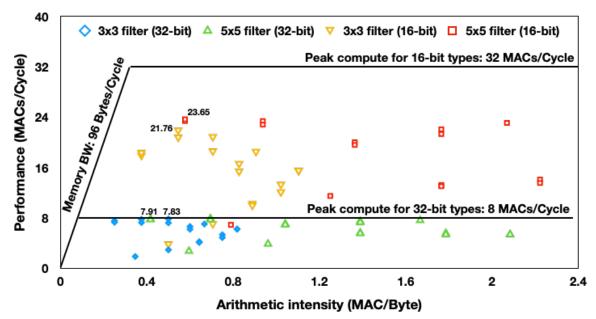

| 6.8  | Comparison of our approach with auto-tuner against the available expert-<br>written codes for CONV2D operation with $3\times3$ and $5\times5$ filters                                                                                                                                                                                                                                  |

| 6.9  | Roof-line graphs of four workloads considered in Figure 6.8, where each data point is a schedule explored by the auto-tuner                                                                                                                                                                                                                                                            |

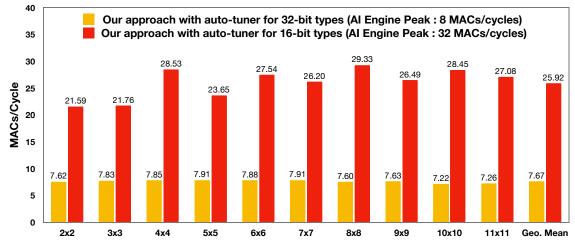

| 6.10 | Performance of our approach generated codes for CONV2D workloads of<br>Computer Vision over filter sizes from 2 to 11                                                                                                                                                                                                                                                                  |

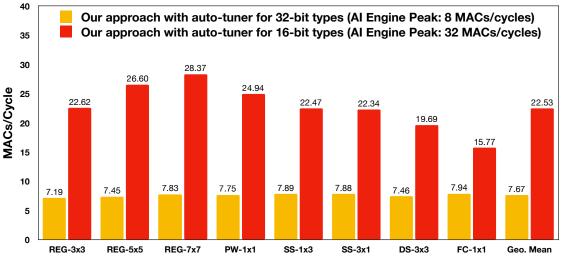

| 6.11 | Performance of our approach generated codes for CONV2D workloads (shown in Table 6.7) of Deep Learning                                                                                                                                                                                                                                                                                 |

| 6.12 | Data-layouts of input and weight tensors of the 16-bit REG-3x3 workload (Table 6.7), to enable the fusion of 1D logical vector multiplications along the channels, thereby avoiding the padding required for weights                                                                                                                                                                   |

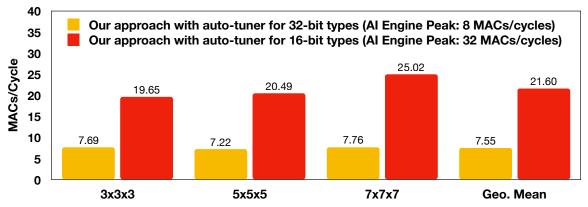

| 6.13 | Performance of our approach generated codes for CONV3D workloads with weight sizes as $3x3x3$ , $5x5x5$ , $7x7x7$                                                                                                                                                                                                                                                                      |

| 7.1  | Overview of a single Emu node (figure source: [53]), where a dotted circle represents a nodelet. Note that, the co-location of the narrow channel memory unit (NCDRAM) with gossamer cores makes the overall Emu system a near memory system                                                                                                                                           |

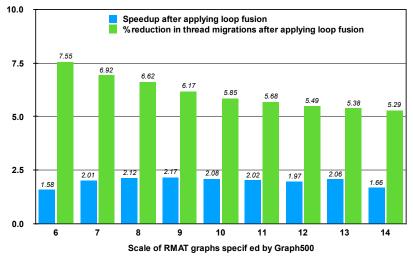

| 7.2  | Speedup over the original conductance algorithm on a single Emu node (8 nodelets) and % reductions in thread migrations after applying loop fusion. 125                                                                                                                                                                                                                                |

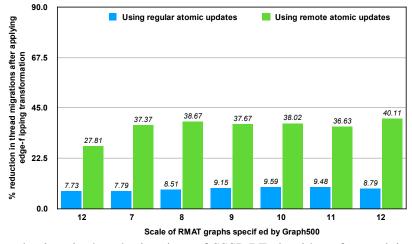

| 7.3 | % reductions in thread migrations of SSSP-BF algorithm after applying<br>edge flipping with regular atomic updates and with remote atomic updates<br>on a single node (8 nodelets) of Emu Chick |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

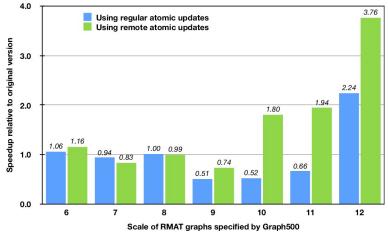

| 7.4 | Speedup of SSSP-BF algorithm on a single Emu node (8 nodelets) after applying edge flipping with regular atomic updates and with remote updates. 127                                            |

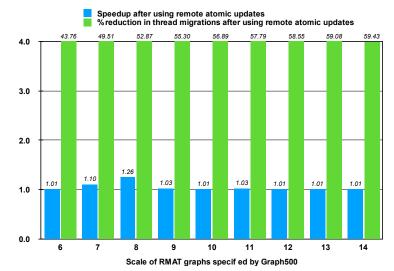

| 7.5 | Speedup over the original triangle counting implementation on a single Emu node (8 nodelets) and % reductions in thread migrations after using remote atomic updates                            |

#### SUMMARY

Computer hardware is undergoing a major disruption as we approach the end of Moore's law, in the form of new advancements to general-purpose and domain-specific parallel architectures. Contemporaneously, the demand for higher performance is broadening across multiple application domains ranging from scientific computing applications to deep learning and graph analytics. These trends raise a plethora of challenges to the de-facto approach to achieving higher performance, namely application development using high-performance libraries. Some of the challenges include porting/adapting to multiple parallel architectures, supporting rapidly advancing domains, and also inhibiting optimizations across library calls. Hence, there is a renewed focus on advancing optimizing compilers from industry and academia to address the above trends, but doing so requires enabling compilers to work effectively on a wide range of applications and also to exploit current and future parallel architectures better. As summarized below, this thesis focuses on compiler advancements for current and future hardware trends.

First, we observe that software with explicit parallelism for general-purpose multi-core CPUs and GPUs is on the rise, but the foundation of current compiler frameworks is based on optimizing sequential code. Our approach uses explicit parallelism specified by the programmer as logical parallelism to refine the conservative dependence analysis inherent in compilers (arising from the presence of program constructs such as pointer aliasing, unknown function calls, non-affine subscript expressions, recursion, and unstructured control flow). This approach makes it possible to combine user-specified parallelism and compiler-generated parallelism in a new unified polyhedral compilation framework (PoPP).

Second, despite the fact that compiler technologies for automatic vectorization for general-purpose vector processing (SIMD) units have been under development for over four decades, there are still considerable gaps in the capabilities of modern compilers to perform automatic vectorization. One such gap can be found in the handling of loops with dependence cycles that involve memory-based anti (write-after-read) and output (write-after-write) dependences. A significant limitation in past work is the lack of a unified formulation that synergistically integrates multiple storage transformations to break the cycles and further unify the formulation with loop transformations to enable vectorization. To address this limitation, we propose the PolySIMD approach.

Third, the efficiency of domain-specific spatial accelerators for Deep Learning (DL) solutions depends heavily on the compiler's ability to generate optimized mappings or code for various DL operators (building blocks of DL models, e.g., CONV2D, GEMM) on the accelerator's compute and memory resources. However, the rapid emergence of new operators and new accelerators pose two key challenges/requirements to the existing compilers: 1) Ability to perform fine-grained reasoning of various algorithmic aspects of the new operators and also complex hardware structures of the new accelerators to achieve peak performance, and 2) Ability to quickly explore the enormous space of possible mappings involving various partitioning schemes, loop transformations, and data-layout choices, yet achieving high-performance and energy efficiency. To address these challenges, we introduced a data-centric compiler "Marvel" for optimizing DL operators onto flexible spatial accelerators. We also introduced a high-performance vectorizing compiler "Vyasa" for optimizing tensors convolutions on specialized SIMD units of Xilinx AI Engine.

Finally, with the emergence of a domain-specific thread migratory architecture (EMU) to address the locality wall, we developed thread-migration aware compiler optimizations to enhance the performance of graph analytics on the EMU machine. Our preliminary evaluation of compiler optimizations such as node fusion and edge flipping demonstrate a significant benefit relative to the original programs.

## CHAPTER 1 INTRODUCTION

Traditionally, computational science and engineering (CSE) applications such as largescale climate prediction, computational fluid dynamics, high-dimensional tensor contractions, have dominated the need for performance to advance research in science and engineering. However, the demand for high performance is broadening across multiple application domains with the advent of big data and machine learning in the current era. For example, large-scale graph processing has become an essential application domain for high performance because of the prevalence of large graph data size from social networks [1, 2]. In the last few years, Deep Learning (DL) became a promising solution to many of the learning tasks such as real-time speech recognition, computer vision, health intelligence, self-driving cars [3, 4, 5]. These DL solutions also require higher performance because of their longer training time and also tight latency constraints in the inference.

Parallel computer architectures refer to a class of computer processors with multiple compute units connected via interconnection networks and a memory hierarchy. Some of the popular parallel computer architectures are multi-core CPUs, SIMD units, and GPUs. Figure 1.1 presents a quick forty-year overview of the processor performance, and we briefly describe the parallel architecture evolution from 2004.

Figure 1.1: 40 years of process performance (taken from [6, 7]).

**Parallel architectures evolution from 2004:** The inability to increase single CPU clock frequency within a power budget because of the breakdown of Dennard's scaling (power wall [8]) has resulted in the emergence of *multi-core processors*, and enabled Moore's law

(doubling transistor count per every two years) [9] to extend further. Each of these cores employs either simultaneous multi-threading (SMT) [10] or fine-grained multi-threading [11] to provide thread-level parallelism. Also, *vector processing units*, i.e., Single Instruction Multiple Data (SIMD) units, are integrated with the individual CPU cores to provide data-parallelism.

The multi-core solution was a partial response to address the end of Dennard's scaling, and the solution quickly resulted in the utilization wall<sup>1</sup>, i.e., the percentage of a multi-core chip that can actively switch drops exponentially due to power constraints. As a result, multiple approaches have emerged to address the utilization wall. Some of the notable approaches are: 1) *Light-weight and simpler general-purpose* cores (e.g., Intel KNL, GPG-PUs), 2) *Domain-specific accelerators* tailored to optimizing a set of specific computations (e.g., DNN accelerators, specialized SIMD units), and 3) *Heterogeneous* processors incorporating both light-weight general-purpose cores and domain-specific accelerators (e.g., Xilinx Versal [7]).

Unlike processor architectures, recently, applications have started posing walls to achieve higher performance on the existing parallel architectures, for example, locality wall [14] with the rise of memory-intensive applications (e.g., large scale graph analytics), where computation is dominated by data access, movement, and little reuse during the computation. To address the locality wall, multiple approaches have started emerging, and some of the noted approaches are: 1) *Migratory thread-based architecture* (e.g., EMU [15]) with near-memories, 2) *3D stacked near-memory systems* (e.g., HMC Micron [16]), and 3) *Custom accelerators for domain-specific memory-intensive applications* (e.g., ExTensor [17] for sparse linear algebra).

**General-Purpose and Domain-Specific Parallel Architectures:** Since we are reaching the end of Moore's law, significant disruption is underway in computer hardware as processors strive to extend, and go beyond, the end-game of Moore's Law. The Industry and Academia are pushing the boundaries of maximum peak performance and energy efficiency of parallel hardware by 1) making the general-purpose processors lightweight and increasing its count on a chip, and 2) building custom domain-specific accelerators to accelerate specific sets of computations.

Majorly, there are three approaches to achieving the higher performance of applications on parallel architectures -1) Ninja (expert) programmers, 2) High-performance libraries, and 3) Optimizing compilers. Ninja programmers have an in-depth knowledge of architec-

<sup>&</sup>lt;sup>1</sup>The utilization wall is also referred to as dark silicon [12, 13] in the literature.

ture, including various hardware intricacies, and optimize a given application very well on that particular architecture. However, this approach requires a significant investment effort to port it to other architectures, and this becomes even more daunting with the proliferation of more architectures as we approach towards the end of Moore's law.

Library-based approach, the de-facto approach, lets a programmer/developer compose an application using high-performance library primitives, which are generally provided by the hardware vendors (e.g., Intel MKL) and tuned for their particular architectures. However, this approach can yield sub-optimal performance of the entire application, because these library calls are black boxes to programmers/compilers to perform optimizations across library calls. Also, with applications rapidly evolving (e.g., DNN models and their operators) and their input sizes varying drastically (e.g., DNN layer sizes), it is tough for the hardware vendors to cope with such a rapid change and provide a library that can provide high-performance across all the inputs (e.g., Intel MKL DGEMM kernel can yield lower performance on skewed matrix shapes).

Optimizing compilers is another approach to achieve performance across a variety of parallel architectures and includes optimizations to maximize parallelism and memory locality using loop dependence analysis and transformations [18, 19, 20, 21, 22, 23, 24]. Using this approach, programmers/application developers can become less concerned about intricacies of the performance optimizations and underlying architecture details, unlike Ninja programmers. Since the optimizing compilers generally have back-ends for multiple target architectures (e.g., LLVM), the portability issues to other architectures can be alleviated using this approach. Also, optimizing compilers can customize their optimization techniques based on application input sizes, and also help in optimizing the rapidly evolving applications/kernels (e.g., DNN models and their operators), unlike the library-based approaches [25]. Even though there are numerous benefits of using the optimizing compilers still require advancements in program analysis, code transformations, and code generation to exploit better the advancements in both the general-purpose and domain-specific parallel architectures as part of the hardware disruption.

#### **1.1 Thesis Statement**

"Given the increasing demand for performance across multiple application domains and the major disruptions in future computer hardware as we approach the end of Moore's Law, our thesis is that advances in compiler optimizations, via newer analyses, transformations, mapping space exploration strategies, and code generation techniques, are critical for enabling a wide range of applications to exploit future advances in both general-purpose and domain-specific parallel architectures."

#### 1.2 Contributions

In this section, we outline our contributions in advancing compiler optimizations via newer analyses, transformations, mapping space exploration strategies, and code generation techniques to achieve higher performance on general-purpose and domain-specific parallel architectures.

1) Polyhedral optimizations of explicitly-parallel programs for general-purpose multicore processors: Most of the compiler frameworks treat explicit-parallelism of an input program either as unknown library calls or ignore them and perform dependence analysis to enable optimizations. Additionally, the compilers perform conservative dependence analysis in the presence of unanalyzable constructs such as pointer aliasing, unknown function calls, non-affine expressions, recursion, and unstructured control flow. These unanalyzable constructs can limit the applicability of transformations even though they are legal to apply. Our work is motivated by the observation that software with explicit parallelism is on the rise. Our approach uses the explicit parallelism specified by the programmer as a logical parallelism. Then, our approach refines the conservative dependences with partial execution order from the explicit parallelism to enable a broader set of loop transformations, compared to what might have been possible if the input program is sequential.

A summary of our approach (PoPP – Polyhedral optimizer for Parallel Programs) [26, 27] is as follows. We first enable conservative dependence analysis of a given region of code by introducing dummy variables that can work with any polyhedral tool that supports *access functions*. After obtaining conservative dependences, the Fourier-Motzkin elimination method is used to remove all dummy variables. Next, we identify happens-before relations from the explicitly parallel constructs, notably parallel loops and tasks, and intersect with conservative dependences. The resulting set of dependences is then passed on to a polyhedral optimization tool, such as PolyAST, to enable the transformation of explicitly-parallel programs with unanalyzable data accesses.

We evaluate our approach using twelve OpenMP benchmark programs from the KAS-TORS and Rodinia benchmark suites. We show that 1) these benchmarks contain unanalyzable data accesses that prevent polyhedral frameworks from performing exact dependence analysis, 2) explicit parallelism can help mitigate the imprecision, and 3) polyhedral transformations with the resulting dependences can further improve the performance of manually-parallelized OpenMP programs. Our experimental results show performance improvements for these OpenMP programs on a 12-core Intel Westmere platform and a 24-core IBM Power8 platform.

2) Unification of multiple storage transformations with loop optimizations for enhanced vectorization on general-purpose vector processors (SIMD/GPUs): Despite the fact that compiler technologies for automatic vectorization have been under development for over four decades, there are still considerable gaps in the capabilities of modern compilers to perform automatic vectorization for SIMD units. One such gap can be found in the handling of loops with dependence cycles that involve memory-based anti (write-after-read) and output (write-after-write) dependences. Past approaches, such as variable renaming and variable expansion, break such dependences. However, the past work suffers from three key limitations: 1) Lack of a unified framework that synergistically integrates multiple storage transformations, 2) Lack of support for bounding the additional space required to break memory-based dependences, and 3) Lack of support for integrating these storage transformations with other code transformations (e.g., statement reordering) to enable vectorization.

We address the three limitations above by integrating both Source Variable Renaming (SoVR) and Sink Variable Renaming (SiVR) transformations into a unified formulation, and by formalizing the "cycle-breaking" problem as a minimum weighted set cover optimization problem. To the best of our knowledge, our work (PolySIMD) [28] is the first to formalize an optimal solution (reflecting best execution time) for cycle breaking that simultaneously considers both SoVR and SiVR transformations, thereby enhancing vectorization and reducing storage expansion relative to performing the transformations independently.

We implemented our approach in PPCG, a state-of-the-art optimization framework for loop transformations, and evaluated it on eleven kernels from the TSVC benchmark suite. Our experimental results show a geometric mean performance improvement of  $4.61 \times$  on an Intel Xeon Phi (KNL) machine relative to the optimized performance obtained by Intel's ICC v17.0 product compiler. Further, our results demonstrate a geometric mean performance improvement of  $1.08 \times$  and  $1.14 \times$  on the Intel Xeon Phi (KNL) and Nvidia Tesla V100 (Volta) platforms relative to past work that only performs the SiVR transformation [29], and of  $1.57 \times$  and  $1.22 \times$  on both platforms relative to past work on using both SiVR and SoVR transformations [30].

3) Data-centric compiler for deep learning operators onto domain-specific DNN spatial accelerators: The efficiency of a spatial DNN accelerator depends heavily on the compiler and its cost model ability to generate optimized mappings for various operators of DNN models on the accelerator's compute and memory resources. A significant difference between the compilers for spatial accelerators and CPUs/GPUs is the need for "accurate" cost models for finding optimal mappings reflecting best latency and energy efficiency. This is because spatial accelerator's performance is sensitive to the mapping parameters, for, e.g., a small change in the tile size or degree of parallelism would drastically change the latency or energy efficiency numbers. However, existing cost models lack a formal boundary over the operators for precise and tractable analysis, which poses adaptability challenges for new DNN operators. To address this challenge, we leverage the recently introduced Maestro Data-Centric (MDC) notation. We develop a formal understanding of DNN operators whose mappings can be described in the MDC notation because any mapping adhering to the notation is always analyzable by the MDC's cost model. Furthermore, we introduce a transformation for translating mappings into the MDC notation for exploring the mapping space.

Searching for the optimal mappings reflecting best latency and energy efficiency is challenging because of the large space of mappings, and this challenge gets exacerbated with new operators and diverse accelerator configurations. To address this challenge, we propose a decoupled off-chip/on-chip approach that decomposes the mapping space into off-chip and on-chip subspaces, and first optimizes the off-chip subspace followed by the on-chip subspace. The motivation for this decomposition is to dramatically reduce the size of the search space and prioritize the optimization of off-chip data movement, which is 2-3 orders of magnitude more than the on-chip data movement. We implemented our approach in a tool called *Marvel*, and another significant benefit of our approach is that it applies to any DNN operator conformable with the MDC notation. In addition, our approach works by leveraging two state-of-the-art cost models to explore the two subspaces – a classical distinct-block (DB) locality cost model for the off-chip subspace, and a state-of-the-art DNN accelerator behavioral cost model, MAESTRO, for the on-chip subspace.

Overall, our approach reduced the mapping space by an  $O(10^{10})$  factor for the four major CNN models (AlexNet, VGG16, ResNet50, MobileNetV2), while generating mappings that demonstrate a geometric mean performance improvement of  $10.25 \times$  higher throughput

and  $2.01 \times$  lower energy consumption compared with three state-of-the-art mapping styles from past work. We also evaluated our approach over the GEMM, LSTM, and MLP work-loads and compared them with the optimizers from past work.

4) High-performance vectorizing compiler for tensor convolutions on the Xilinx AI Engine (domain-specific 2D SIMD processor): There is a strong resurgence of interest in improving vector processing (SIMD) units due to the significant energy efficiency benefits of using SIMD parallelism. There is an emphasis on specializing SIMD units to improve further energy efficiency benefits for specific domains such as Machine learning, Computer Vision, and 5G Wireless. An important specialization, which is referred to as "2D vector SIMD datapath" [31, 32, 33], is the ability of each vector lane to execute more than one scalar operation and to chain the results from one operation to another. Another specialization includes the removal of expensive data permutation units (e.g., shuffle units) [34, 35] and instead introduce sophisticated, programmable interconnection networks (a.k.a shuffle networks) between the SIMD datapath and vector register file to support the required data permutation patterns [36, 33]. Xilinx's AI Engine is a recent industry example of energyefficient vector processing that includes novel support for 2D SIMD datapaths and shuffle interconnection network. The current approach to programming the AI Engine relies on a C/C++ API for vector intrinsics. While an advance over assembly-level programming, it requires the programmer to specify a number of low-level operations based on detailed knowledge of the hardware.

To address these challenges, we introduce *Vyasa*, a new programming system that extends the Halide DSL compiler to generate code for the AI Engine automatically. We evaluated Vyasa on 36 CONV2D and 6 CONV3D workloads and achieved geometric means of 7.6 and 23.3 MACs/cycle for 32-bit and 16-bit operands (which represent 95.9% and 72.8% of the peak performance respectively). For 4 of these workloads for which expert-written codes were available to us, Vyasa demonstrated a geometric mean performance improvement of  $1.10 \times$  with 50× smaller code relative to the expert-written codes. Further, our compiler-generated code achieved a geometric mean performance improvement of  $1.134 \times$  relative to expert-written codes available for two workloads.

5) Thread-migration aware compiler optimizations for graph analytics on threadmigratory domain-specific hardware (EMU): Unlike dense linear algebra applications, graph applications typically suffer from poor performance because of 1) inefficient utilization of memory systems through random memory accesses to graph data, and 2) overhead of executing atomic operations. Hence, there is a rapid growth in improving software and hardware platforms to address the above challenges. One such improvement in the hardware is a realization of the Emu system, a thread migratory and near-memory processor introduced to address applications domains having weak-locality. In the Emu system, a thread responsible for computation on a datum is automatically migrated over to a node where the data resides without any intervention from the programmer. The idea of thread migrations is very well suited to graph applications as memory accesses of the applications are irregular. However, thread migrations can hurt graph applications' performance if overhead from the migrations dominates the benefits achieved through migrations.